# Hybrid Gate Dielectric Materials for Unconventional Electronic Circuitry

Young-Geun Ha,<sup>†,§</sup> Ken Everaerts,<sup>†</sup> Mark C. Hersam,<sup>\*,†,‡</sup> and Tobin J. Marks<sup>\*,†,‡</sup>

<sup>†</sup>Department of Chemistry and the Materials Research Center, Northwestern University, 2145 Sheridan Road, Evanston, Illinois 60208, United States

<sup>‡</sup>Department of Materials Science and Engineering, Northwestern University, 2220 Campus Drive, Evanston, Illinois 60208, United States

<sup>§</sup>Department of Chemistry, Kyonggi University, Suwon, Gyeonggi-Do 443-760, Republic of Korea

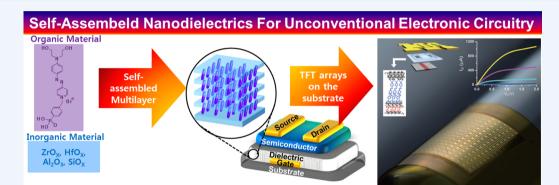

**CONSPECTUS:** Recent advances in semiconductor performance made possible by organic  $\pi$ -electron molecules, carbon-based nanomaterials, and metal oxides have been a central scientific and technological research focus over the past decade in the quest for flexible and transparent electronic products. However, advances in semiconductor materials require corresponding advances in compatible gate dielectric materials, which must exhibit excellent electrical properties such as large capacitance, high breakdown strength, low leakage current density, and mechanical flexibility on arbitrary substrates. Historically, conventional silicon dioxide (SiO<sub>2</sub>) has dominated electronics as the preferred gate dielectric material in complementary metal oxide semiconductor (CMOS) integrated transistor circuitry. However, it does not satisfy many of the performance requirements for the aforementioned semiconductors due to its relatively low dielectric constant and intransigent processability. High-*k* inorganics such as hafnium dioxide (HfO<sub>2</sub>) or zirconium dioxide (ZrO<sub>2</sub>) offer some increases in performance, but scientists have great difficulty depositing these materials as smooth films at temperatures compatible with flexible plastic substrates. While various organic polymers are accessible via chemical synthesis and readily form films from solution, they typically exhibit low capacitances, and the corresponding transistors operate at unacceptably high voltages. More recently, researchers have combined the favorable properties of high-*k* metal oxides and  $\pi$ -electron organics to form processable, structurally well-defined, and robust self-assembled multilayer nanodielectrics, which enable high-performance transistors with a wide variety of unconventional semiconductors.

In this Account, we review recent advances in organic—inorganic hybrid gate dielectrics, fabricated by multilayer self-assembly, and their remarkable synergy with unconventional semiconductors. We first discuss the principals and functional importance of gate dielectric materials in thin-film transistor (TFT) operation. Next, we describe the design, fabrication, properties, and applications of solution-deposited multilayer organic—inorganic hybrid gate dielectrics, using self-assembly techniques, which provide bonding between the organic and inorganic layers. Finally, we discuss approaches for preparing analogous hybrid multilayers by vapor-phase growth and discuss the properties of these materials.

### 1. INTRODUCTION

Thin-film transistors (TFTs) fabricated from unconventional materials and by unconventional methodologies are of interest for future low-cost electronic applications, including RF-ID technologies, sensors, light-emitting diodes (LEDs), liquid crystal/OLED display backplane circuitry, and integrated optoelectronic devices.<sup>1</sup> The attractions of these systems include atomic-level tunability of properties,<sup>2</sup> solution processing via high-throughput roll-to-roll printing,<sup>3</sup> and low temperature (<150 °C) fabrication

compatible with inexpensive, flexible plastic substrates.<sup>4</sup> This approach offers the possibility of inexpensive, large-area, flexible devices processed at far lower substrate temperatures and over far greater areas than conventional silicon-based technologies.<sup>5</sup>

Transistors are the key components used for current modulation and switching in all modern electronics. There are

Received: September 17, 2013 Published: January 15, 2014

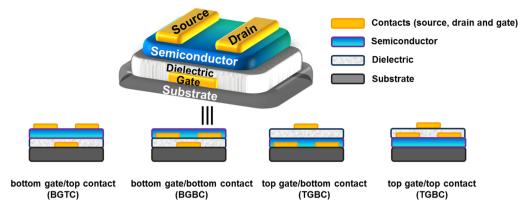

Figure 1. Typical thin-film transistor structures.

three fundamental TFT materials components: electrodes (source, drain, and gate), the semiconductor channel, and the gate dielectric. The arrangement of these components can be classified by the geometry of the gate (i.e., bottom-gate or top-gate) and contacts (i.e., bottom-contact or top-contact), leading to four common device geometries (Figure 1). The basic working principle of TFTs is that the current between source and drain contacts ( $I_{\rm DS}$ ) in saturation is modulated by the gate bias ( $V_{\rm G}$ ) according to eq 1 where W and L are the channel width and length,  $C_i$  is the dielectric capacitance per unit area,  $\mu$  is the charge carrier mobility,  $V_{\rm G}$  is the gate voltage, and  $V_{\rm T}$  is the threshold voltage.

$$I_{\rm DS} = \frac{W}{2L} \mu C_i (V_{\rm G} - V_{\rm T})^2$$

(1)

Over the past two decades, solution-processable organic, inorganic, and nanomaterial semiconductors have attracted much attention due to the aforementioned advantages over traditional silicon technologies.<sup>6</sup> Despite recent progress, a principal limitation of these semiconductors when integrated with conventional gate dielectric materials  $(SiO_2)$  is their low carrier mobilities, well below those of high-performance siliconbased materials.<sup>7</sup> These inferior transport characteristics, due primarily to SiO<sub>2</sub> defects such as charged oxide impurities, remote interface phonons, and interface traps, require additional source-drain  $(V_{DS})$  to source-gate  $(V_G)$  bias (voltage) as compensation to achieve a target transistor current  $(I_{DS})$ , which in turn increases power consumption. For low power applications such as RF-ID tags, flat panel displays, and portable electronics, it is mandatory to achieve high TFT drain currents  $(I_{\rm DS})$  at the lowest operating voltages possible (ideally <4 V). According to eq 1, a feasible approach to achieve this is to increase the capacitance of the gate dielectric.

$$C_i = \varepsilon_0 \frac{k}{d} \tag{2}$$

Note from eq 2 that increasing the dielectric constant (k) or decreasing the thickness (d) of the gate dielectric layer offers this additional capacitance. An increase in the k/d ratio is also necessary for efficient device size reduction (scaling), which supports low-power TFT operation. Importantly, from eq 1, enhancing the semiconductor mobility  $(\mu)$ , potentially enabled by a high-quality dielectric, can also increase the drain current for a given voltage, in addition to increases originating from capacitance.

High-*k* inorganic metal oxide (MO) dielectric films, such as  $HfO_2$ ,  $Al_2O_3$ , or  $ZrO_2$  have been grown by a variety of methods

and exhibit well-defined dielectric properties.<sup>8</sup> However, highquality MO dielectric films typically require high processing temperatures and/or capital-intensive vacuum deposition techniques to ensure acceptably low current leakage. Furthermore, most high-k MO films, particularly if crystalline, are generally too brittle for applications requiring flexible substrates. Thus, the demand for flexible plastic substrates and low-cost fabrication cannot easily be met with conventional high-k inorganic-only dielectrics. In contrast, many organic polymeric materials have processability advantages due to their mechanical flexibility, solubility, and capacity to form near-amorphous microstructures. Most importantly, they form films from solution and at low temperatures, enabling compatibility with solutionbased coating/patterning techniques. However, typical polymer gate dielectrics have limits due to their relatively low dielectric constants and modest thermal stability.

In contrast, organic—inorganic hybrids can, in optimum cases, synergistically combine the useful and distinctive properties of both classes of materials. Hybrid materials provide the optical, electrical, and environmental durability of inorganic materials, and the mechanical flexibility and properties tunability of  $\pi$ -electron organics. Combining these characteristics can thereby compensate for deficiencies in dielectric properties or processability, while often enhancing thermal and mechanical properties.<sup>10</sup> Notable examples of organic—inorganic hybrid gate dielectrics include using self-assembled monolayers (SAMs) with ultra-thin metal oxide films,<sup>5,11</sup> hybrid polymeric nanocomposite or bilayer materials,<sup>12</sup> and hybrid self-assembled multilayer structures.<sup>14,15,28,29,31,32</sup> Among these, self-assembled multilayers composed of well-defined organic precursor layers and inorganic metal oxide thin-films enable realization of new classes of robust functional materials with high degrees of order and structural control at the molecular level.

This Account focuses on the design, synthesis, properties tuning, and implementation of organic—inorganic multilayer gate dielectrics for TFTs fabricated with a variety of semiconductor classes. Recent applications and developments using hybrid materials in this area are summarized and analyzed. The discussion focuses on the two major approaches for preparing self-assembled multilayer hybrid dielectrics: solution and vapor phase deposition.

# 2. HYBRID MULTILAYER DIELECTRICS BY SOLUTION PHASE DEPOSITION

A key to utilizing layered organic—inorganic hybrid multilayers for electronics applications is the ability to prepare high-quality hybrid multilayers in the simplest, most reliable manner.

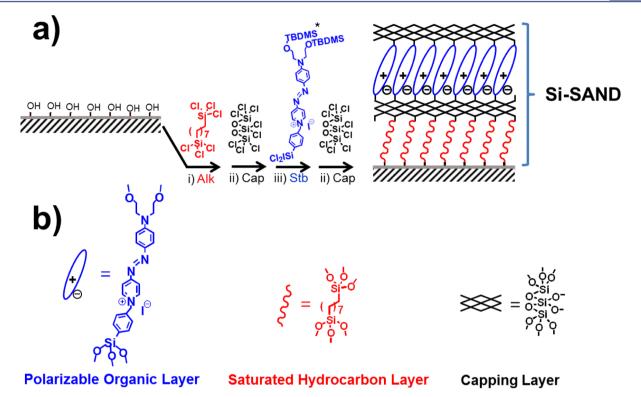

**Figure 2.** (a) Schematic representation of silane-based self-assembled nanodielectric (Si-SAND) multilayers, which can be sequentially deposited from solution. (b) Individual components of Si-SANDs. \*TBDMS = *tert*-butyldimethylsilyl.

Layer-by-layer solution-based film growth using well-defined precursors enables the self-limiting assembly (self-assembly) of diverse, highly ordered functional materials. A variety of self-assembly approaches have been reported, often based on siloxane<sup>13</sup> or on metal–ligand coordination chemistry.<sup>14</sup>

#### 2.1. Silane-Based Self-Assembled Nanodielectrics (Si-SAND)

First-generation hybrid gate dielectrics, referred to as silanebased self-assembled nanodielectrics (Si-SANDs), are grown by stepwise multilayer assembly using organosilane reagents (Figure 2).<sup>15</sup> The resulting hybrid materials contain 3D crosslinked thin-film networks grown from solution via self-limiting sequential deposition of chlorosilane building blocks, including saturated hydrocarbon layers, highly polarizable "push-pull"  $\pi$ -electron organic layers, and octachlorotrisiloxane-(Cl<sub>3</sub>SiO-(SiCl<sub>2</sub>)OSiCl<sub>3</sub>)-derived capping layers. Capacitance-voltage (C-V) measurements on metal-insulator-semiconductor (MIS) structures reveal a range of capacitance (390-710 nF  $cm^{-2}$  at 10<sup>2</sup> Hz) depending on the combination of the organic and inorganic components. These Si-SANDs have several noteworthy characteristics that greatly enhance TFT performance: (1) large capacitance that reduces TFT operating voltage; (2) high thermal/chemical stability (e.g., 350 °C stability in air) compatible with a range of semiconductor processing conditions and operating environments; (3) marked tendency to suppress trapped charges at the dielectric-semiconductor interface.

With Si-SAND gate dielectrics, impressive performance enhancements vs SiO<sub>2</sub> gate dielectrics are observed for ZnO, SnO<sub>2</sub>, and In<sub>2</sub>O<sub>3</sub> nanowire TFTs, with mobilities in the range 170–1500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (typically ~10× greater than those with SiO<sub>2</sub>).<sup>16</sup> Furthermore, arrays of Si-SAND/nanowire TFTs enable the fabrication of transparent active-matrix monochrome OLED displays.<sup>17</sup> Si-SAND was also investigated in TFTs with unpurified random network single-walled carbon nanotubes

(SWCNTs) as the semiconductor,<sup>18</sup> achieving respectable mobilities ( $\mu = 5.6 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) and low threshold voltages  $(V_{\rm T} = 0.2 \text{ V})$  with greatly reduced hysteresis and  $V_{\rm T}$  shift versus devices with SiO<sub>2</sub> dielectrics. In the area of transparent oxide semiconductors (TOSs), Si-SAND compatibility was demonstrated by growing In<sub>2</sub>O<sub>3</sub> thin films at 25 °C by ion-assisted deposition of both the semiconductor and source/drain layers (grown under different O<sub>2</sub> pressures) to enable high mobility, low voltage, and optically transparent ("invisible") TFTs:  $^{19}\mu$  =  $120 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , interfacial trap density  $D = 10^{11} \text{ cm}^{-2}$ ,  $V_T = 0.1$ ,  $I_{\rm ON}/I_{\rm OFF} = 10^5$ , and subthreshold swing (SS) = 0.090 V decade<sup>-1</sup> with nearly hysteresis-free response. These metrics can be compared with SiO<sub>2</sub>-gated devices where  $\mu = 10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $I_{\rm ON}/I_{\rm OFF} = 10^5$ . In subsequent studies, the same fabrication procedures using poly(ethyleneterephthalate) (PET) substrates afforded fully transparent and flexible In2O3 TFTs exhibiting  $\mu = 20 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $I_{\text{ON}}/I_{\text{OFF}} = 10^{4.20}$  These results suggest new strategies for achieving "invisible" electronic circuitry as exemplified by polycrystalline In<sub>2</sub>O<sub>3</sub> transistor arrays with hybrid dielectrics.

In related work, mechanically flexible, low operating voltage transistor logic gates (NOT, NAND, and NOR gates) were demonstrated using printed silicon nanomembranes with Si-SAND on thin plastic substrates (Kapton).<sup>21</sup> These transistors exhibit effective linear mobilities of ~680 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>,  $I_{\rm ON}/I_{\rm OFF}$  > 10<sup>7</sup>, gate leakage current densities <2.8 × 10<sup>-7</sup> A/cm<sup>2</sup>, and SS ≈ 0.120 V decade<sup>-1</sup>. Furthermore, Si-SAND/Si inverters show voltage gains as high as 4.8, and simple digital logic gates (NAND and NOR gates) demonstrate the possible application of these materials for flexible, high-performance digital integrated circuits.

In regard to device fabrication via solution processing, Si-SAND dielectrics were shown to be compatible with semiconducting CdSe films grown by chemical bath deposition

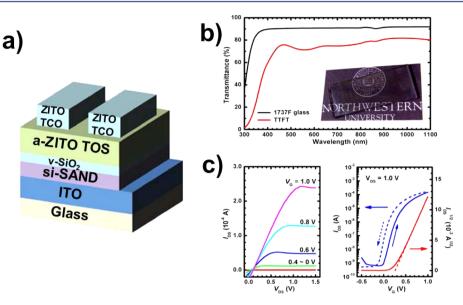

**Figure 3.** (a) Architecture of transparent a-ZITO (Zn–In–Sn–O) TFT fabricated on glass with the materials indicated. (b) Transmission optical spectrum of transparent array of TFTs (the inset shows a photograph of the TFT array on the glass). (c) Output plot showing good saturation characteristics with low operating voltages, and transfer plot showing minimal hysteresis. TOS = transparent oxide semiconductor; TOC = transparent oxide conductor; ITO = indium tin oxide. Adapted with permission from ref 26. Copyright 2011 Wiley-VCH Verlag GmbH & Co. KGaA.

(CBD) and annealed at 400–500 °C.<sup>22</sup> The mobilities of these films are ~57 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with large  $I_{\rm ON}/I_{\rm OFF}$  (~10<sup>5</sup>) and SS as low as 0.26 V decade<sup>-1</sup>. In regard to solution-processed oxides, spin-coating In<sub>2</sub>O<sub>3</sub> sol–gel precursor solutions on Si-SAND and annealing at 400 °C yields polycrystalline In<sub>2</sub>O<sub>3</sub> films with TFT mobilities as high as ~44 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with  $I_{\rm ON}/I_{\rm OFF} > 10^7$  at <4 V operating bias.<sup>23</sup> Similarly, amorphous In–Sn–O films ([In]/[In + Sn] = 0.7) can be prepared by an analogous solution route and afford Si-SAND-based TFTs with  $\mu \approx 10-20$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> after annealing at relatively low temperature (250 °C).<sup>24</sup> In a subsequent paper, a detailed study of the Zn–In–Sn–O system yielded smooth, amorphous films with optimal transport properties after annealing at 400 °C. Here, a-Zn–In–Sn–O (a-ZITO) TFTs fabricated on Si-SAND exhibit  $\mu \approx 90$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>,  $I_{\rm ON}/I_{\rm OFF} \approx 10^5$ , SS  $\approx 0.2$  V decade<sup>-1</sup>, and operation at <2 V.<sup>25</sup>

Pulsed laser deposition (PLD) is a versatile film growth technique, and in related studies, it was shown that cross-linked, hexachlorodisiloxane (Cl<sub>3</sub>SiOSiCl<sub>3</sub>)-derived SiO<sub>2</sub> coatings greatly enhance Si-SAND resistance to PLD laser plume degradation while growing overlying oxide films on this dielectric, thereby expanding Si-SAND compatibility with a broad range of semiconductors.<sup>26</sup> For example, integrating Si-SAND and PLD-derived a-ZITO TOS films with a transparent conducting oxide (TCO) gate and source/drain electrodes yields optically transparent TFTs (Figure 3) with superlative performance parameters:  $\mu \approx 140 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $I_{\text{ON}} > 10^{-4} \text{ A}$ ,  $I_{\text{ON}}/I_{\text{OFF}} \approx 10^5$ , SS  $\approx 0.13$  V decade<sup>-1</sup>, and operating voltage  $\approx 1.0$  V.

Regarding the understanding of Si-SAND function, transport and computational studies indicate that the saturated hydrocarbon and SiO<sub>x</sub> layers impart the insulating characteristics (transport via tunneling), while the  $\pi$ -electron layers provide the k (tunneling at low temperatures, hopping transport at higher temperatures).<sup>27</sup> Furthermore, quantitative analysis of Si-SAND dielectric breakdown via Weibull techniques shows that the breakdown statistics of these unconventional molecular dielectrics can be as uniform as those of conventional inorganic dielectrics.<sup>28</sup>

#### 2.2. Zirconia-Based Self-Assembled Multilayer Nanodielectrics (Zr-SANDs)

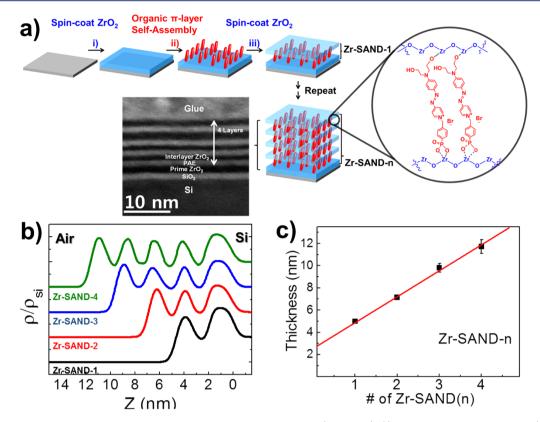

In a second solution processed multilayer approach, zirconiaphosphonate self-assembled nanodielectrics (Zr-SANDs) incorporating highly polarizable phosphonic acid-based  $\pi$ -electron (PAE) layers interleaved with nanoscopic high-*k* zirconium oxide (ZrO<sub>2</sub>) layers were synthesized and characterized (Figure 4).<sup>29</sup> The synthetic reagents are well-suited for self-assembly processes in ambient conditions, yielding well-structured multilayers, where ultra-thin ZrO<sub>2</sub> primer layers are spin-coated on hydroxyl-functionalized Si substrates, followed by baking and immersion in a phosphonic-acid (PA) functionalized precursor solution for self-assembly of the organic layer. Repeating this sequence results in structurally regular multilayers with tunable thicknesses (5–12 nm) characterized by X-ray reflectivity (XRR) and cross-sectional scanning transmission electron microscopy (STEM).

This flexible Zr-SAND synthetic approach offers high capacitance (465-750 nF/cm<sup>2</sup>), low leakage current density  $(\sim 10^{-7} \text{A/cm}^2 \text{ at } 2 \text{ MV/cm})$ , and thermal stability at 400 °C in ambient atmosphere. Zr-SAND dielectrics function effectively with both organic and inorganic semiconductors, exhibiting excellent TFT performance in terms of mobility (pentacene ~0.38 and Zn–Sn–O ~3.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and  $I_{\rm ON}/I_{\rm OFF}$  (>10<sup>6</sup>) at low operating bias  $(< \pm 4 \text{ V})$ .<sup>27</sup> Moreover, these dielectrics can be modified by various PA-based hydrocarbon monolayers to further enhance TFT performance for n- or p-type organic semiconductors.<sup>27</sup> In related work, the compatibility of Zr-SAND with amorphous and polycrystalline In-Y-O (IYO) films grown via a low-temperature (200-300 °C) solution process utilizing "combustion" precursors was shown to afford low voltage (2 V) IYO TFTs with  $\mu = 7.3 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ( $T_{\text{process}} = 300 \text{ °C}$ ) and 5.0 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> ( $T_{\text{process}} = 250 \text{ °C}$ ), and  $I_{\text{ON}}/I_{\text{OFF}} > 10^{5.30}$  This integration of combustion-derived amorphous oxide films with hybrid nanodielectrics points to future opportunities in novel materials implementation at temperatures compatible with flexible plastic substrates.

**Figure 4.** (a) Fabrication procedure for Zr-phosphonate self-assembled nanodielectric (Zr-SAND): (i) spin-coat  $ZrO_2$  for prime layer; (ii) self-assembly of phosphonic acid-based organic  $\pi$ -electron layer; (i) spin-coat  $ZrO_2$  for interlayer (inset shows cross-sectional TEM image of the Zr-SAND film interface; labels indicate the layer identities). (b) Specular X-ray reflectivity (XRR)-derived electron density profiles (normalized to  $\rho_{si}$ ) as a function of height *z* above the Si substrate. (c) XRR-derived film thickness (nm) data as a function of the number of Zr-SAND prepared via the procedure of panel a. Adapted with permission from ref 29. Copyright 2011 American Chemical Society.

The uniformity of the dielectric breakdown voltage distribution for several thicknesses of Zr-SANDs was characterized using Weibull statistical analysis.<sup>31</sup> Two regimes of breakdown behavior are observed: thicker multilayers (>5 nm) are well described by the Weibull distribution, while thinner multilayers ( $\leq$ 5 nm thick) exhibit bends in the Weibull plot of breakdown voltage, suggesting multiple characteristic mechanisms. Interestingly, both the degree of uniformity and the effective dielectric breakdown field are observed to be greater for thinner layers than for thicker layers of Zr-SAND, implying that the thinner layer structure is more promising for device applications.

# 2.3. Hafinia-Based Self-Assembled Nanodielectrics (Hf-SANDs)

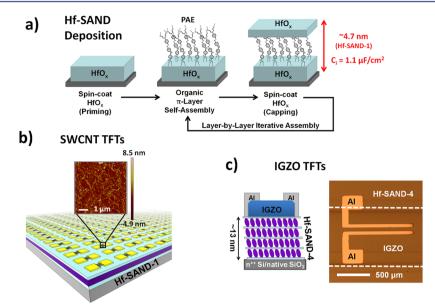

Hafnium oxide (HfO<sub>x</sub>)-based SAND materials (Hf-SAND) were recently investigated in an effort to increase the *k*-enhancing PAE  $\pi$ -organic layer surface coverage via the greater HfO<sub>x</sub> affinity for acids versus that of ZrO<sub>x</sub>, and to expand the library of compatible oxide semiconductors (Figure 5a).<sup>32</sup> An earlier TFT study of Si-SAND with SWCNTs<sup>16</sup> motivated their use to probe the dielectric characteristics of Hf-SAND. Advances in SWCNT purification<sup>33</sup> along with the very large capacitance of 1.1  $\mu$ F/cm<sup>2</sup> for single-layer Hf-SAND determined in this work (~10× greater than that in the original Si-SAND), enabled high-performance semiconductor-enriched SWCNT TFTs (Figure 5b). Outstanding device performance was obtained with  $I_{\rm DS} \approx 10$  mA using only  $V_{\rm DS} \approx 1$  V and  $V_{\rm G} \approx 3$  V, offering record transconductance ( $g_{\rm m}$ ) of 5.5 mS and record-matching SS of ~0.15 V decade<sup>-1,34</sup> indicative of low interface trap density. Gate leakage current was limited to ~2 nA at +2 V  $V_{\rm G}$  even with large  $I_{\rm DS}$  in the TFT channel. The highly uniform and conformal coating possible with HfO<sub>x</sub> and the organic nanolayers provides smooth interfaces of ~2 Å rms roughness with limited pinhole defects, such that large-area TFT devices (850  $\mu$ m  $\times$  250  $\mu$ m) can reliably be produced on a 4.7 nm thick Hf-SAND layer (Figure 5b). Near record intrinsic mobilities ( $\mu_{\rm IN}$ ) of ~140 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> demonstrate the ability of Hf-SAND to efficiently drive dense SWCNT networks (15 SWCNTs/ $\mu$ m), historically difficult for globally back-gated SWCNT TFT geometries.<sup>35</sup> The excellent capacitive coupling of the semiconductor and gate offers simultaneously large  $I_{\rm ON}/I_{\rm OFF}$  (~10<sup>6</sup>),  $I_{\rm DS}$ ,  $\mu$ , and unprecedented  $g_{\rm m}^{.36,37}$

Finally, the low temperature (<150 °C) solution-based growth of Hf-SAND opens the possibility of using inkjet-printable semiconducting In-Ga-Zn-O (IGZO) for TFT fabrication.<sup>38</sup> Thus, a new low-temperature "combustion" chemistry route to IGZO thin films was developed that produces high-mobility films at  $T_{\text{process}}$  = 300 °C. Using SiO<sub>2</sub> and in-house grown atomic layer deposition (ALD) HfO2 as control dielectrics, Hf-SAND-gated, inkjet-printed IGZO TFTs (Figure 5c) demonstrate a record electron mobility  $\mu = 20.6 \pm 4.3$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, steep SS  $\approx 0.15$  V decade<sup>-1</sup>, near zero  $V_{\rm T}$ , and the ability to achieve  $I_{\rm DS} \approx 1$  mA with <2 V  $V_{\rm DS}$  and <2 V  $V_{\rm G}$ . This  $\mu$  is nearly 4× greater than the control devices (~5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), where the origin of the mobility enhancement is attributed to low levels of dielectric fixed charge, reducing Coulombic scattering of carriers in the IGZO semiconductor layer.<sup>39</sup> Thus, Hf-SAND not only offers the large capacitance possible with other ALD-grown high-koxide materials, but limits the impact of oxide fixed charge,

Figure 5. (a) Solution-phase Hf-SAND self-assembly procedure. (b) Schematic SWCNT/Hf-SAND TFT arrays, with inset atomic force micrograph showing a random network of SWCNTs in the TFT channel. (c) IGZO TFTs produced by inkjet printing (right) utilizing the multilayer variant of Hf-SAND schematically shown on the left. Panels a and b adapted with permission from ref 32 and panel c from ref 39. Copyright 2013 American Chemical Society.

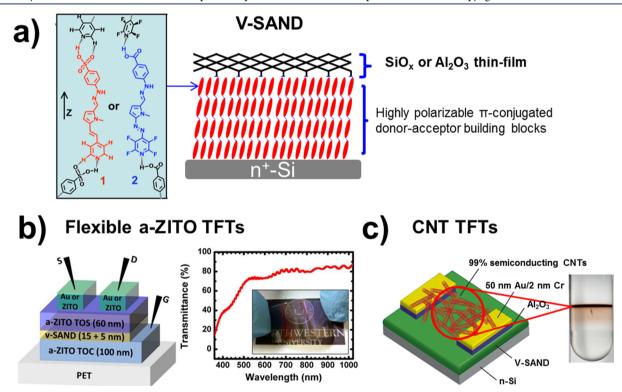

**Figure 6.** (a) Schematic representation of vapor-deposited self-assembled nanodielectrics (V-SAND) and chemical structures of organic components **1** and **2**. (b) Architecture and transmission optical spectrum (inset, a photograph of the TFT array bent over a printed Northwestern University seal) of transparent flexible a-ZITO thin-film transistor fabricated on a plastic substrate with the indicated materials. Adapted with permission from ref 42. Copyright 2011 Wiley-VCH Verlag GmbH & Co. KGaA. (c) Schematic of random SWCNT TFT fabricated on V-SAND using high purity (99%) semiconducting carbon nanotube film. Adapted with permission from ref 35. Copyright 2012 American Chemical Society.

interface traps, and remote polar phonons that are otherwise disruptive to semiconductor carrier transport.

## 3. HYBRID MULTILAYER DIELECTRICS BY VAPOR PHASE DEPOSITION

A complementary approach to accessing multilayer hybrid dielectrics with large gate capacitances is possible via solventfree vapor-phase self-assembly, V-SAND (Figure 6). V-SANDs can be grown with precise thickness control and combine layers of highly polarizable  $\pi$ -conjugated donor—acceptor building blocks, self-assembled via hydrogen bonding, with ultra-thin layers of vapor-phase deposited SiO<sub>x</sub> or ALD-derived Al<sub>2</sub>O<sub>3</sub> to enhance stability and dielectric characteristics. Note that the dielectric response of the two types of molecular constituents,

| dielectric | capacitance<br>(nF/cm <sup>2</sup> ) | $I_{\rm G}{}^a$                                              | semiconductor <sup>b</sup>           | $\mu \; ({\rm cm}^2  {\rm V}^{-1}  {\rm s}^{-1})$ | $I_{ m ON}/I_{ m OFF}$ | $V_{\mathrm{T}}\left(\mathrm{V} ight)$ | SS<br>(V decade <sup>-1</sup> ) | ref |

|------------|--------------------------------------|--------------------------------------------------------------|--------------------------------------|---------------------------------------------------|------------------------|----------------------------------------|---------------------------------|-----|

| Si-SAND    | ~180                                 | $10^{-8} \text{ A/cm}^2$                                     | ZnO NW                               | ~198                                              | 10 <sup>4</sup>        | -0.4                                   |                                 | 16a |

|            | ~180                                 | 30–40 pA (4 V)                                               | In <sub>2</sub> O <sub>3</sub> NW    | ~1450                                             | 10 <sup>6</sup>        | 0.0                                    |                                 | 16b |

|            | ~180                                 |                                                              | SnO <sub>2</sub> NW                  | ~172                                              | 10 <sup>6</sup>        | -1.9                                   |                                 | 16c |

|            | ~170                                 | ~10 nA (1 V)                                                 | SWCNT                                | 5.6                                               | 107                    | 0.2                                    |                                 | 18  |

|            |                                      |                                                              | $In_2O_3$ thin-film (IAD)            | ~120                                              | 10 <sup>5</sup>        | 0.1                                    | 0.09                            | 19  |

|            |                                      |                                                              | $In_2O_3$ thin-film (IAD) flexible   | 20                                                | 10 <sup>4</sup>        |                                        |                                 | 20  |

|            | ~180                                 | 3.9 pA (1 V)                                                 | Si-Nanomembrane                      | ~680                                              | 10 <sup>7</sup>        | -1.1                                   | 0.12                            | 21  |

|            | ~270                                 | $1 \times 10^{-7} \text{ A/cm}^2 (4 \text{ V})$              | CdSe (CBD)                           | 57                                                | 10 <sup>5</sup>        | 2.5                                    | 0.26                            | 22  |

|            |                                      |                                                              | $In_2O_3$ (SC)                       | 44                                                | 10 <sup>6</sup>        | 2.2                                    | 0.3                             | 23  |

|            |                                      |                                                              | ITO (SC)                             | 10-20                                             | 10 <sup>4</sup>        |                                        |                                 | 24  |

|            |                                      |                                                              | ZITO (SC)                            | 90                                                | 10 <sup>5</sup>        |                                        | 0.2                             | 25  |

|            | ~200                                 | $1 \times 10^{-6} \text{A/cm}^2 \left(1 \text{MV/cm}\right)$ | ZITO (PLD)                           | ~140                                              | 10 <sup>5</sup>        | 0.2                                    | 0.13                            | 26  |

| Zr-SAND    | 398                                  | $\sim 3 \times 10^{-7} \text{ A/cm}^2$                       | pentacene (PVD)                      | 0.74                                              | 10 <sup>6</sup>        | -0.6                                   |                                 | 29  |

|            | 398                                  | $\sim 3 \times 10^{-7} \text{ A/cm}^2$                       | $PDIF-CN_2$ (PVD)                    | 0.79                                              | $10^{4}$               | 0.01                                   |                                 | 29  |

|            | 465                                  | $\sim 3 \times 10^{-7} \text{ A/cm}^2$                       | ZTO (SC)                             | 3.5                                               | 10 <sup>7</sup>        | -1.1                                   | 0.12                            | 29  |

|            | 450                                  |                                                              | IYO (SC)                             | 7.3 (300)                                         | 10 <sup>5</sup>        |                                        |                                 | 30  |

|            |                                      |                                                              |                                      | 5.0 (250)                                         |                        |                                        |                                 |     |

| Hf-SAND    | 1100                                 | $\sim 1 \times 10^{-7} \text{ A/cm}^2$                       | SWCNT (99% semiconducting<br>purity) | 137                                               | 10 <sup>6</sup>        | 0.5                                    | 0.15                            | 32  |

|            | 630                                  | <10 <sup>-8</sup> A (2 V)                                    | IGZO (IJ)                            | 20.6                                              | 10 <sup>7</sup>        | $\sim 0$                               | 0.19                            | 39  |

| V-SAND     | 390                                  | $10^{-5} - 10^{-7} \text{ A/cm}^2 (2 \text{ V})$             | pentacene                            | 2.4                                               | 10 <sup>5</sup>        | 1                                      |                                 | 40  |

|            | 220                                  | $10^{-6}$ -10 <sup>-7</sup> A/cm <sup>2</sup> (1 MV/cm)      | ZITO (PLD)                           | 110                                               | 10 <sup>4</sup>        | 0.2                                    | 0.13                            | 41  |

|            | 630                                  | $10^{-7} \text{ A/cm}^2 (1 \text{ V})$                       | SWCNT (99% semiconducting purity)    | 147                                               | 10 <sup>5</sup>        | -1.1                                   | 0.15                            | 35  |

Table 1. Summary of Dielectric and TFT Characteristics for SANDs with Various Semiconductors

<sup>*a*</sup>Measured at 2 MV/cm, unless noted in parentheses. <sup>*b*</sup>IAD = ion-assisted deposition; CBD = chemical bath deposition; PLD = pulsed laser deposition; PVD, physical vapor deposition; SC = spin-coating. IJ = inkjet-printing.

**1** and **2**, are enhanced by (i) their ability to self-assemble via head-to-tail hydrogen-bonding and (ii) molecular polarizabilities that are optimized<sup>40</sup> via computation-assisted design. It was demonstrated that the MIS and TFT device electrical properties are sensitive to the changes in microstructural organization such as introducing organic—inorganic alternating and nonalternating arrangements.<sup>41</sup> Pentacene TFTs fabricated with V-SAND exhibit large mobilities, ~3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and  $I_{\rm ON}/I_{\rm OFF} \approx 10^5$  for optimized TFT performance. More importantly, this computation-assisted dielectric provides key molecular and thin-film structural information on how to design even higher performance gate dielectric films using self-assembled materials. V-SAND dielectrics are evidently promising for future flexible organic electronics requiring low-temperature, solvent-free deposition conditions.

The compatibility of V-SAND with amorphous TOS thin films was demonstrated by combining Zn–In–Sn–O (ZITO) thin films grown by pulsed-laser deposition (PLD) from a Zn<sub>0.33</sub>In<sub>1.40</sub>Sn<sub>0.27</sub>O<sub>3</sub> target at 25 °C under O<sub>2</sub> partial pressure. Completely transparent TFTs with good mechanical flexibility were realized by integrating an a-ZITO channel, a TCO electrode, and V-SAND on flexible PET substrates to enable fully transparent TFTs<sup>42</sup> exhibiting 110 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> mobility, 1.0 V operation,  $I_{\rm ON}/I_{\rm OFF} \approx 10^4$ ,  $V_{\rm T} = 0.2$  V, and SS = 0.13 V decade<sup>-1</sup>.

In a subsequent study, V-SAND gate dielectrics were integrated with high-purity semiconducting SWCNT films as the active layer to achieve TFT performance unconstrained by traditional trade-offs, such as trading large  $I_{\rm DS}$  or  $\mu$  for low  $I_{\rm ON}/I_{\rm OFF}$  or steep SS for low overall  $I_{\rm DS}$ .<sup>33</sup> Thus, the resulting devices simultaneously exhibit <4 V operating voltages, SS = 0.15 V decade<sup>-1</sup>, high normalized on-state conductance (8.5  $\mu$ S/ $\mu$ m), high normalized transconductance (6.5  $\mu$ S/ $\mu$ m), and high

intrinsic field-effect mobility (147 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) with high  $I_{\rm ON}/I_{\rm OFF} = 5 \times 10^5$  in ambient conditions. This landmark and recordsetting process of combining hybrid gate dielectrics with semiconducting SWCNTs is compatible with low-temperature, large-area processing, thus offering great potential in low-power TFT-based electronics. These devices also exhibit negligible hysteresis in transfer characteristics, unlike those fabricated with conventional oxide dielectrics, and avoid the ambipolarity that increases power consumption for SWCNT TFT circuits based on ionic gel-based dielectrics.<sup>43</sup>

#### 4. CONCLUSIONS

Novel molecule-scale organic—inorganic hybrid materials useful for overcoming the performance and processing limitations of conventional gate dielectric oxides (e.g.  $SiO_2$ ) have been discussed in this Account. SANDs have proven compatibility with a wide range of unconventional semiconductors, often leading to enhanced transport properties (Table 1), with an advantageous component modularity affording ready adaptations to specific semiconductors and applications. This contribution also illustrates how reduced transparency, processability, and environmental stability, makes SAND concepts of unique value to the future of high-performance unconventional electronics, including mechanically flexible, optically transparent, and high throughput roll-to-roll printed digital circuitry.

Future SAND-semiconductor integration, process/deposition refinement, and component synthesis ( $\pi$ -organic layer) strategies not only offer research opportunities but are needed to support continual advances in semiconductor and electronics applications. For example, efforts aimed at tuning surface density and packing motif of the  $\pi$ -electron constituents by selection of

#### **Accounts of Chemical Research**

specific metal oxide layers is a promising avenue just beginning to be explored and may dramatically affect layer dielectric constant and overall dielectric performance. Furthermore, the synthesis of new  $\pi$ -electron constituents may offer additional benefits in enhancing dipolar polarizability, surface organization, or assembly rates. Thus, the intensive research efforts devoted to date in new semiconductors motivate complementary efforts in gate dielectric materials that offer compatible manufacture with the semiconductor, including solution or vapor phase processing, affording SAND-like materials relevant for electronic technologies.

## AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: t-marks@northwestern.edu.

\*E-mail: m-hersam@northwestern.edu.

## Notes

The authors declare no competing financial interest.

#### **Biographies**

Young-Geun Ha was born in 1975. He graduated from Korea University where he obtained his B.S. in chemistry (2003) and M.S. in physical chemistry (2005) with Prof. Jong-Ho Choi. He received his Ph.D. degree in chemistry at Northwestern University (2011) with Prof. Tobin Marks. His thesis focused on the design, synthesis, and characterization of novel organic—inorganic hybrid dielectric materials for TFTs. He is currently an Assistant Professor at Kyonggi University (South Korea). He has published 26 research articles and holds 5 patents. His research interests include organic/inorganic semiconductors and dielectrics for thin-film transistors and self-assembled monolayers and multilayers.

Ken Everaerts was born in 1983 in Leuven, Belgium. After immigrating with his parents to the U.S.A. at a young age, he attended St. Cloud State University (MN) and earned his B.S. in Chemistry in 2007. He is currently a Ph.D. graduate student under mentorship of Profs. Tobin J. Marks and Mark C. Hersam, working on high capacitance dielectric materials for next-generation semiconductor TFTs. He has coauthored two research papers and received a Hierarchical Materials Fellowship from the Northwestern University Graduate School in 2010. His research interests include developing new materials and integration strategies using nanomaterial, organic, and inorganic electronic materials for next-generation electronics.

Mark C. Hersam is the Bette and Neison Harris Chair in Teaching Excellence and Professor of Materials Science and Engineering, Chemistry, and Medicine at Northwestern University. He earned a B.S. in Electrical Engineering from the University of Illinois at Urbana– Champaign (UIUC) in 1996, M.Phil. in Physics from the University of Cambridge in 1997, and a Ph.D. in Electrical Engineering from UIUC in 2000. His research interests include nanofabrication, scanning probe microscopy, semiconductor surfaces, and carbon nanomaterials. Dr. Hersam is a Fellow of MRS, AVS, APS, and SPIE and serves as Associate Editor of *ACS Nano*.

**Tobin J. Marks** is Vladimir N. Ipatieff Professor of Chemistry and Professor of Materials Science and Engineering at Northwestern University. He received his B.S. from the University of Maryland in 1966 and Ph.D. from MIT in 1971. Among his 125 awards and named lectureships, he was awarded the National Medal of Science in 2006. He is a Fellow of the American Academy of Arts and Sciences and a Member of the U.S. National Academies of Sciences and Engineering. His research interests include organic and inorganic electronic and optoelectronic materials, organometallic chemistry and catalysis, chemical vapor deposition, electronic ceramics, and polymer science.

#### ACKNOWLEDGMENTS

We thank the ONR MURI Program (N00014-11-1-0690), AFOSR (FA9550-08-1-0331), the Northwestern NSF MRSEC (DMR-1121262), and Polyera Corp. for support of this research.

#### REFERENCES

(1) (a) Forrest, S. R.; Thompson, M. E. Introduction: Organic Electronics and Optoelectronics. *Chem. Rev.* 2007, 107, 923–925.

(b) Facchetti, A. Semiconductors for Organic Transistors. *Mater. Today* 2007, 10, 28–37. (c) Kagan, C. R., Andry, P., Eds. *Thin-Film Transistors*; Marcel Dekker, Inc.: New York, 2003.

(2) (a) Arias, A. C.; MacKenzie, J. D.; McCulloch, I.; Rivnay, J.; Salleo, A. Materials and Applications for Large Area Electronics: Solution-Based Approaches. *Chem. Rev.* **2010**, *110*, 3–24. (b) Pal, B. N.; Dhar, B. M.; See, K. C.; Katz, H. E. Solution-Deposited Sodium beta-Alumina Gate Dielectrics for Low-Voltage and Transparent Field-Effect Transistors. *Nat. Mater.* **2009**, *8*, 898–903. (c) Murphy, A. R.; Frechet, J. M. J. Organic Semiconducting Oligomers for Use in Thin Film Transistors. *Chem. Rev.* **2007**, *107*, 1066–1096.

(3) (a) Allard, S.; Forster, M.; Souharce, B.; Thiem, H.; Scherf, U. Organic Semiconductors for Solution-Processable Field-Effect Transistors (OFETs). Angew. Chem., Int. Ed. 2008, 47, 4070-98.

(b) Sirringhaus, H. Device Physics of Solution-Processed Organic Field-Effect Transistors. Adv. Mater. 2005, 17, 2411-2425. (c) Sirringhaus, H.; Kawase, T.; Friend, R. H.; Shimoda, T.; Inbasekaran, M.; Wu, W.; Woo, E. P. High-Resolution Inkjet Printing of All-Polymer Transistor Circuits. Science 2000, 290, 2123-2126.

(4) (a) Marks, T. J. Materials for Organic and Hybrid Inorganic/ Organic Electronics. *MRS Bull.* **2010**, *35*, 1018–1027. (b) Roberts, M. E.; Mannsfeld, S. C. B.; Queralto, N.; Reese, C.; Locklin, J.; Knoll, W.; Bao, Z. N. Water-Stable Organic Transistors and Their Application in Chemical and Biological Sensors. *Proc. Natl. Acad. Sci. U.S.A.* **2008**, *105*, 12134–9. (c) Cho, J. H.; Lee, J.; Xia, Y.; Kim, B.; He, Y. Y.; Renn, M. J.; Lodge, T. P.; Frisbie, C. D. Printable Ion-Gel Gate Dielectrics for Low-Voltage Polymer Thin-Film Transistors on Plastic. *Nat. Mater.* **2008**, *7*, 900–906.

(5) Klauk, H.; Zschieschang, U.; Pflaum, J.; Halik, M. Ultralow-Power Organic Complementary Circuits. *Nature* **2007**, *445*, 745–748.

(6) (a) Usta, H.; Facchetti, A.; Marks, T. J. n-Channel Semiconductor Materials Design for Organic Complementary Circuits. *Acc. Chem. Res.* **2011**, *44*, 501–510. (b) Yan, H.; Chen, Z.; Zheng, Y.; Newman, C.; Quinn, J. R.; Dötz, F.; Kastler, M.; Facchetti, A. A High-Mobility Electron-Transporting Polymer for Printed Transistors. *Nature* **2009**, *457*, 679–686.

(7) (a) Ortiz, R. P.; Facchetti, A.; Marks, T. J. High-k Organic, Inorganic, and Hybrid Dielectrics for Low-Voltage Organic Field-Effect Transistors. *Chem. Rev.* **2010**, *110*, 205–239. (b) Facchetti, A.; Yoon, M. H.; Marks, T. J. Gate Dielectrics for Organic Field-Effect Transistors: New Opportunities for Organic Electronics. *Adv. Mater.* **2005**, *17*, 1705–1725.

(8) (a) Kim, M.-G.; Hennek, J. W.; Kim, H. S.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Exploratory Combustion Synthesis: Amorphous Indium Yttrium Oxide for Thin-Film Transistors. *J. Am. Chem. Soc.* **2012**, *134*, 9593–9596. (b) Kim, M.-G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Low-Temperature Fabrication of High-Performance Metal Oxide Thin-Film Electronics via Combustion Processing. *Nat. Mater.* **2011**, *10*, 382–388. (c) Acton, O.; Ting, G.; Ma, H.; Ka, J. W.; Yip, H. L.; Tucker, N. M.; Jen, A. K. Y.  $\pi$ - $\sigma$ -Phosphonic Acid Organic Monolayer/Sol–Gel Hafnium Oxide Hybrid Dielectrics for Low-Voltage Organic Transistors. *Adv. Mater.* **2008**, *20*, 3697–3701. (9) Veres, J.; Ogier, S.; Lloyd, G.; de Leeuw, D. Gate Insulators in Organic Field-Effect Transistors. *Chem. Mater.* **2004**, *16*, 4543–4555.

(10) DiBenedetto, S. A.; Ratner, M. A.; Facchetti, A.; Marks, T. J. Molecular Self-Assembled Monolayers and Multilayers for Organic and Unconventional Inorganic Thin-Film Transistor Applications. *Adv. Mater.* **2009**, *21*, 1407–1433.

(11) (a) Ma, H.; Acton, O.; Hutchins, D. O.; Cernetic, N.; Jen, A. K.-Y. Multifunctional Phosphonic Acid Self-Assembled Monolayers on Metal Oxides as Dielectrics, Interface Modification Layers and Semiconductors for Low-Voltage High-Performance Organic Field-Effect Transistors. *Phys. Chem. Chem. Phys.* **2012**, *14*, 14110–14126. (b) Park, Y. M.; Daniel, J.; Heeney, M.; Salleo, A. Room-Temperature Fabrication of Ultrathin Oxide Gate Dielectrics for Low-Voltage Operation of Organic Field-Effect Transistors. *Adv. Mater.* **2011**, *23*, 971–974.

(12) (a) Kim, J.; Lim, S.; Kim, Y. Solution-Based TiO<sub>2</sub>-Polymer Composite Dielectric for Low Operating Voltage OTFTs. J. Am. Chem. Soc. **2010**, 132, 14721–14723. (b) Ha, Y.-G.; Jeong, S.; Wu, J.; Kim, M.; Vinayak, D.; Facchetti, A.; Marks, T. J. Flexible Low-Voltage Organic Transistors Enabled by Low Temperature Ambient Solution-Processed Inorganic/Organic Hybrid Gate Dielectric Materials. J. Am. Chem. Soc. **2010**, 132, 17426–17434. (c) Hwang, D.; Kim, C.; Choi, J.; Lee, K.; Park, J.; Kim, E.; Baik, H.; Kim, J.; Im, S. Polymer/YO<sub>x</sub> Hybrid-Sandwich Gate Dielectrics for Semitransparent Pentacene Thin-Film Transistors Operating Under 5 V. Adv. Mater. **2006**, 18, 2299–2303.

(13) Ulman, A. Formation and Structure of Self-Assembled Monolayers. *Chem. Rev.* **1996**, *96*, 1533–1554.

(14) (a) Ha, Y. G.; Facchetti, A.; Marks, T. J. Push–Pull  $\pi$ -Electron Phosphonic-Acid-Based Self-Assembled Multilayer Nanodielectrics Fabricated in Ambient for Organic Transistors. *Chem. Mater.* **2009**, *21*, 1173–1175. (b) Katz, H. E.; Scheller, G.; Putvinski, T. M.; Schilling, M. L.; Wilson, W. L.; Chidsey, C. E. D. Polar Orientation of Dyes in Robust Multilayers by Zirconium Phosphate-Phosphonate Interlayers. *Science* **1991**, *254*, 1485–1487.

(15) Yoon, M. H.; Facchetti, A.; Marks, T. J. *σ*-*π* Molecular Dielectric Multilayers for Low-Voltage Organic Thin-Film Transistors. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 4678–4682.

(16) (a) Ju, S.; Ha, Y. G.; Kim, S.; Facchetti, A.; Mohammadi, S.; Marks, T. J.; Janes, D. B. Interface Studies of ZnO Nanowire Transistors Using Low-Frequency Noise and Temperature-Dependent I-V Measurements. *Appl. Phys. Lett.* **2008**, *92*, No. 022104. (b) Ju, S.; Ishikawa, F.; Chen, P.; Chang, H.-K.; Zhou, C.; Ha, Y. G.; Liu, J.; Facchetti, A.; Marks, T. J.; Janes, D. B. High Performance In2O3 Nanowire Transistors Using Organic Gate Nanodielectrics. *Appl. Phys. Lett.* **2008**, *92*, No. 22210. (c) Ju, S.; Chen, P.; Zhou, C.; Ha, Y. G.; Facchetti, A.; Marks, T. J.; Kim, S. K.; Mohammadi, S.; Janes, D. B. 1/f Noise of SnO2 Nanowire Transistors. *Appl. Phys. Lett.* **2008**, *92*, No. 243120. (d) Ju, S.; Lee, K.; Janes, D. B.; Yoon, M.-H.; Facchetti, A.; Marks, T. J. Low Operating Voltage Single ZnO Nanowire Field-Effect Transistors Enabled by Self-Assembled Organic Gate Nanodielectrics. *Nano Lett.* **2005**, *5*, 2281– 2286.

(17) (a) Chen, P.-C.; Shen, G.; Chen, H.; Ha, Y.-G.; Wu, C.; Sukcharoenchoke, S.; Fu, Y.; Liu, J.; Facchetti, A.; Marks, T. J.; Thompson, M. C.; Zhou, C. High-Performance Single-Crystalline Arsenic-Doped Indium Oxide Nanowires and Self-Assembled Gate Dielectrics for Transparent Thin Film Transistors and Active Matrix Organic Light-Emitting Diode Displays. ACS Nano 2009, 3, 3383– 3390. (b) Ju, S.; Li, J.; Liu, J.; Chen, P. C.; Ha, Y.; Ishikawa, F.; Chang, H.; Zhou, C.; Faccheti, A.; Janes, D. B.; Marks, T. J. Transparent Active Matrix Organic Light-Emitting Diode Displays Driven By Nanowire Transistor Circuitry. Nano Lett. 2008, 8, 997–1004.

(18) Hur, S.-H.; Yoon, M.-H.; Gaur, A.; Facchetti, A.; Marks, T. J.; Rogers, J. A. Organic Nanodielectrics for Low Voltage Carbon Nanotube Thin Film Transistors and Complementary Logic Gates. *J. Am. Chem. Soc.* **2005**, *127*, 13808–13809.

(19) Wang, L.; Yoon, M.-H.; Lu, G.; Yang, Y.; Facchetti, A.; Marks, T. J. High-Performance Transparent Inorganic-Organic Hybrid Thin-Film n-Type Transistors. *Nat. Mater.* **2006**, *5*, 893–900.

(20) Wang, L.; Yoon, M.-H.; Lu, G.; Yang, Y.; Facchetti, A.; Marks, T. J. Flexible Inorganic/Organic Hybrid Thin-Film Transistors Using All-Transparent Component Materials. *Adv. Mater.* **2007**, *19*, 3252–3256.

(21) Kim, H.-S.; Won, S. M.; Ha, Y.-G.; Facchetti, A.; Marks, T. J.; Rogers, J. A. Self-Assembled Nanodielectrics and Silicon Nanomembranes for Low Voltage, Flexible Transistors, And Logic Gates on Plastic Substrates. *Appl. Phys. Lett.* **2009**, *95*, No. 183504.

(22) Byrne, P. D.; Facchetti, A.; Marks, T. J. High-Performance Thin-Film Transistors from Solution-Processed Cadmium Selenide and a Self-Assembled Multilayer Gate Dielectric. *Adv. Mater.* **2008**, *20*, 2319–2324.

(23) Kim, H. S.; Byrne, P. D.; Facchetti, A.; Marks, T. J. High Performance Solution-Processed Indium Oxide Thin-Film Transistors. *J. Am. Chem. Soc.* **2008**, *130*, 12580–12581.

(24) Kim, H. S.; Kim, M.-G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Low-Temperature Solution-Processed Amorphous Indium Tin Oxide Field-Effect Transistors. *J. Am. Chem. Soc.* **2009**, *131*, 10826–10827.

(25) Kim, M.-G.; Kim, H. S.; Ha, Y.-G.; He, J.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. High-Performance Solution-Processed Amorphous Zinc-Indium-Tin Oxide Thin-Film Transistors. *J. Am. Chem. Soc.* **2010**, *132*, 10352–10364.

(26) Liu, J.; Buchholz, D. B.; Ha, Y.-G.; Xie, S.; Dravid, V. P.; Chang, R. P. H.; Facchetti, A.; Marks, T. J. Reinforced Self-Assembled Nanodielectrics for High-Performance Transparent Thin Film Transistors. *Adv. Mater.* **2011**, *23*, 992–997.

(27) DiBenedetto, S. A.; Facchetti, A.; Ratner, M. A.; Marks, T. J. Charge Conduction and Breakdown Mechanisms in Self-Assembled Nanodielectrics. *J. Am. Chem. Soc.* **2009**, *131*, 7158–7168.

(28) Schlitz, R. A.; Yoon, K. H.; Fredin, L. A.; Ha, Y.-G.; Ratner, M. A.; Marks, T. J.; Lauhon, L. J. Weibull Analysis of Dielectric Breakdown in a Self-Assembled Nanodielectric for Organic Transistors. *J. Phys. Chem. Lett.* **2010**, *1*, 3292–3297.

(29) Ha, Y.-G.; Emery, J. D.; Bedzyk, M. J.; Usta, H.; Facchetti, A.; Marks, T. J. Solution-Deposited Organic-Inorganic Hybrid Multilayer Gate Dielectrics. Design, Synthesis, Microstructures, and Electrical Properties, with Thin-Film Transistors. *J. Am. Chem. Soc.* **2011**, *133*, 10239–10250.

(30) Hennek, J. W.; Kim, M.-G.; Kanatzidis, M. G.; Facchetti, A.; Marks, T. J. Exploratory Combustion Synthesis: Amorphous Indium Yttrium Oxide for Thin-Film Transistors. *J. Am. Chem. Soc.* **2012**, *134*, 9593–9596.

(31) Schlitz, R. A.; Ha, Y.-G.; Marks, T. J.; Lauhon, L. J. Quantitative Statistical Analysis of Dielectric Breakdown in Zirconia-Based Self-Assembled Nanodielectrics. *ACS Nano* **2012**, *6*, 4452–4460.

(32) Everaerts, K.; Emery, J. D.; Jariwala, D.; Karmel, H. J.; Sangwan, V. K.; Prabhumirashi, P. L.; Geier, M. L.; McMorrow, J. J.; Bedzyk, M. J.; Facchetti, A.; Hersam, M. C.; Marks, T. J. Ambient-Processable High Capacitance Hafnia-Organic Self-Assembled Nanodielectrics. *J. Am. Chem. Soc.* **2013**, *135*, 8926–8939.

(33) (a) Seo, J.-W. T.; Yoder, N. L.; Shastry, T. A.; Humes, J. J.; Johns, J. E.; Green, A. A.; Hersam, M. C. Diameter Refinement of Semiconducting Arc Discharge Single-Walled Carbon Nanotubes via Density Gradient Ultracentrifugation. J. Phys. Chem. Lett. 2013, 4, 2805–2810. (b) Tyler, T. P.; Shastry, T. A.; Leever, B. J.; Hersam, M. C. Narrow Diameter Distributions of Metallic Arc Discharge Single-Walled Carbon Nanotubes via Dual-Iteration Density Gradient Ultracentrifugation. Adv. Mater. 2012, 24, 4765-4768. (c) Green, A. A.; Hersam, M. C. Nearly Single-Chirality Single-Walled Carbon Nanotubes Produced via Orthogonal Iterative Density Gradient Ultracentrifugation. Adv. Mater. 2011, 23, 2185-2190. (d) Liu, J.; Hersam, M. C. Recent Developments in Carbon Nanotube Sorting and Selective Growth. MRS Bull. 2010, 35, 315-321. (e) Hersam, M. C. Progress towards Monodisperse Single-Walled Carbon Nanotubes. Nat. Nanotechnol. 2008, 3, 387-394. (f) Arnold, M. S.; Green, A. A.; Hulvat, J. F.; Stupp, S. I.; Hersam, M. C. Sorting Carbon Nanotubes by Electronic Structure Using Density Differentiation. Nat. Nanotechnol. 2006, 1, 60-65.

(34) Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Carbon Nanomaterials for Electronics, Optoelectronics, Photo-voltaics, And Sensing. *Chem. Soc. Rev.* **2013**, *42*, 2824–2860.

(35) Sangwan, V. K.; Ortiz, R. P.; Alaboson, J. M. P.; Emery, J. D.; Bedzyk, M. J.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Fundamental Performance Limits of Carbon Nanotube Thin-Film Transistors Achieved Using Hybrid Molecular Dielectrics. *ACS Nano* **2012**, *6*, 7480–7488.

(36) Avouris, P.; Chen, Z.; Perebeinos, V. Carbon-Based Electronics. *Nat. Nanotechnol.* **2007**, *2*, 605–615.

(37) Avouris, P.; Freitag, M.; Perebeinos, V. Carbon-Nanotube Photonics and Optoelectronics. *Nat. Photonics* **2008**, *2*, 341–350.

(38) Hennek, J. W.; Xia, Y.; Everaerts, K.; Hersam, M. C.; Facchetti, A.; Marks, T. J. Reduced Contact Resistance in Inkjet Printed High-Performance Amorphous Indium Gallium Zinc Oxide Transistors. *ACS Appl. Mater. Interfaces* **2012**, *4*, 1614–1619.

(39) Everaerts, K.; Zeng, L.; Hennek, J. W.; Camacho, D. I.; Jariwala, D.; Bedzyk, M. J.; Hersam, M. C.; Marks, T. J. Printed Indium Gallium Zinc Oxide Transistors. Self-Assembled Nanodielectric Effects on Low-Temperature Combustion Growth and Carrier Mobility. *ACS Appl. Mater. Interfaces* **2013**, *5*, 11884–11893.

(40) DiBenedetto, S. A.; Frattarelli, D.; Ratner, M. A.; Facchetti, A.; Marks, T. J. Vapor Phase Self-Assembly of Molecular Gate Dielectrics for Thin Film Transistors. J. Am. Chem. Soc. **2008**, 130, 7528–7529.

(41) DiBenedetto, S. A.; Frattarelli, D. L.; Facchetti, A.; Ratner, M. A.; Marks, T. J. Structure–Performance Correlations in Vapor Phase Deposited Self-Assembled Nanodielectrics for Organic Field-Effect Transistors. J. Am. Chem. Soc. **2009**, 131, 11080–11090.

(42) Liu, J.; Buchholz, D. B.; Chang, R. P. H.; Facchetti, A.; Marks, T. J. High-Performance Flexible Transparent Thin-Film Transistors Using a Hybrid Gate Dielectric and an Amorphous Zinc Indium Tin Oxide Channel. *Adv. Mater.* **2010**, *22*, 2333–2337.

(43) (a) Ha, M.; Seo, J.-W. T.; Prabhumirashi, P. L.; Zhang, W.; Geier, M. L.; Renn, M. J.; Kim, C. H.; Hersam, M. C.; Frisbie, C. D. Aerosol Jet Printed, Low Voltage, Electrolyte-Gated Carbon Nanotube Ring Oscillators with Sub-5  $\mu$ s Stage Delays. *Nano Lett.* **2013**, *13*, 954–960. (b) Ha, M.; Xia, Y.; Green, A. A.; Zhang, W.; Renn, M. J.; Kim, C. H.; Hersam, M. C.; Frisbie, C. D. Printed, Sub-3V Digital Circuits on Plastic from Aqueous Carbon Nanotube Inks. *ACS Nano* **2010**, *4*, 4388–4395.

#### NOTE ADDED AFTER ASAP PUBLICATION

This manuscript published ASAP on January 15, 2014. The image for Figure 1 was replaced and the revised version was reposted on January 23, 2014.